# Customer Specific Standard Product Approach Enables Platform-Based Design

#### • • • • • • QuickLogic® White Paper

Mobile product system architects and designers face ever-increasing design challenges. Products themselves are becoming more complex, while the schedule and budget for product development are shrinking. The key to meeting these design challenges is to build new products from a common platform that is flexible enough for customization and enhancement. The Customer Specific Standard Product (CSSP) approach that QuickLogic has pioneered provides such platforms.

Consumers are insatiable in their demands for more features and greater sophistication in their mobile products. They also require long battery lifetimes, low product costs and, above all, novelty. This leaves development teams with a demanding task: they need to create complex products that provide both the common features consumers expect as well as unique features that differentiate the product from its competitors.

These feature sets change rapidly. The mobile consumer market is evolving so quickly that the window of opportunity for a new product is less than a year before the next product generation renders it obsolete. New product features are also evolving and proliferating rapidly. A new product feature that becomes popular in the market effectively forces all subsequent product designs to incorporate that feature to remain competitive. For example, the introduction of a touch-screen interface on a popular smartphone in 2007 led to the standardization of touchscreens on all smartphones in less than 12 months. To meet the demand for novelty, design teams must get products to market quickly and often.

Regional variations in the mobile market amplify the challenge. Product design specifics often must vary by region. These variations arise from regulatory and technological differences among regions as well as from differing consumer preferences. Mobile phones for the US market, for instance, differ from cell phones for the Asian market both in the signaling format and the feature sets that consumers expect. Thus, design teams must produce regional variations for their products as quickly and as often as the products themselves.

Along with meeting the need for rapid creation of differentiated products, design teams must work within the constraints of a price-competitive market. Consumers expect that, over time, products with the same features and functions will have lower prices and products that have more features and functions will come in at the same price point as the previous generation. Development team design decisions must therefore result in reduced bills of material and support the streamlined supply chain management needs for cost-effective manufacturing. Further, design teams must operate under tight development budget constraints. Failure to address these market realities results in costs that destroy product profitability.

Traditional design methods cannot meet all these design constraints simultaneously. A design built upon standard, discrete logic components cannot achieve the required price points or small size that mobile devices require. While processors may form part of a design, products that are based on processors alone will not have the needed performance; there are too many functions that need to operate concurrently. The successful design of mobile products requires the use of components that offer highly-integrated standard functions in hard logic while offering the flexibility of adding custom functions for product differentiation.

## **Traditional Design Approaches Fail**

#### **Application-Specific Integrated Circuits (ASICs)**

An ASIC-based design, for instance, can produce components that are relatively inexpensive on a per-unit basis and will yield high-performance and long battery life. They are able to achieve these benefits because ASIC developers can craft a design optimized for performance and battery life while also minimizing die area for lowest cost.

However, there are multiple drawbacks to ASICs that do not make them good choices for many applications.

- Time to Market ASICs take a long time to bring to market often 12 to 18 months from concept to

mass production. In the rapidly-changing mobile device market, only commodity features ones that

customers expect to be in every device are suitable for ASIC implementation. New and innovative features

would take too long to implement in ASIC form, risking late market entry and heavy investment in a function

that may not become popular.

- Cost While per-unit mass production costs may be low, ASICs are best suited for production volumes of many millions due to their large initial investment costs. Wafer masks can cost up to \$1,000,000 US for an individual design, depending on the complexity, process node, and other variables. Often, multiple sets of masks need to be 'cut' for designs as they move through the evaluation phase, increasing development costs. ASIC developers will require a financial return on these development costs, typically done through amortization of these costs on mass production shipments. If production volume is not high enough, the cost per unit can increase to levels that bill of material (BOM) targets cannot support.

#### **Application-Specific Standard Products (ASSPs)**

The ASSP approach tries to improve on ASIC development by offering components that are mostly predesigned, awaiting only software configuration during system boot-up to complete the implementation. This approach is relatively inflexible, however, with limited opportunities for customization. It relies solely on the ASSP vendor to have pre-defined exactly the right mix of capabilities in the silicon. Otherwise, the component will have a silicon area dedicated to functions that are not being used, inflating production costs. Also, while shorter than full ASIC implementations, ASSP design times are still long enough to risk missing market opportunities.

#### **Software Implementations**

Processor-based software implementations offer a high degree of design flexibility by reprogramming the processor to add new functions. They also provide an opportunity for design reuse to speed development of derivative and next-generation devices. While the processor-based approach may have been optimal for early mobile devices, today's designs are so function rich that a pure software-based implementation requires substantial processing capability. That, in turn, demands high power levels that can severely reduce battery operating time. Building peripherals into the processor helps address these concerns, but introduces the same costs and inflexibility issues that ASSPs face.

www.quicklogic.com © 2010 QuickLogic Corporation

# Programmable Logic and Complex Programmable Logic Devices (CPLDs)

Like processors, programmable logic also offers flexibility and design reuse benefits. By itself, however, programmable logic cannot address all mobile device requirements. Primarily, this is due to the fact that SRAM-based programmable logic technologies are notorious for their power demands, high cost and volatility. Typically, the only programmable logic used in a mobile device is in the form of a Complex Programmable Logic Device (CPLD) – a true misnomer since CPLDs can really only handle glue logic and GPIO functionality.

Typically, a mobile device design will use a blend of these techniques. Software handles some functions, ASSPs and other standard product peripherals handle I/O interfaces, and occasionally a CPLD will glue them together. Unfortunately, the blended approach is not particularly cost competitive because it requires too many components and results in a relatively large and inefficient design.

# The CSSP Design Approach

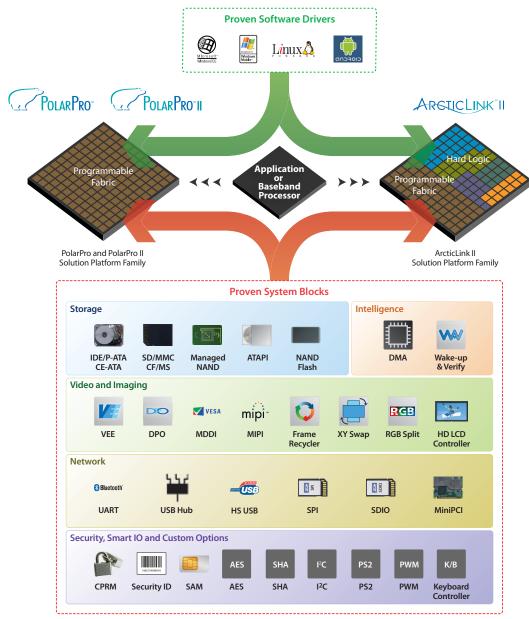

An illustration of the CSSP approach appears in **Figure 1**. The base device, called a CSSP solution platform, is a standard, fully-fabricated component. It contains a number of functions implemented in hard logic blocks that capture a mobile device design's common requirements. These hard logic blocks have tested and proven functionality and offer the high performance, low power, and small silicon footprint expected in a highly-integrated design, but with a significant difference. The hard logic blocks are configurable, able to assume different "personalities," so that a single block can address one of many different requirements.

Figure 1: The CSSP solution platform provides a combination of configurable hard logic blocks and a programmable fabric to blend hard logic performance with design flexibility.

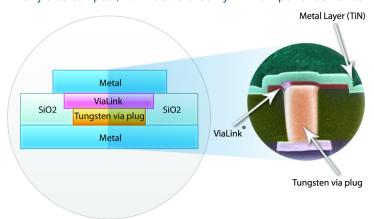

Along with the hard logic blocks, the CSSP offers a programmable fabric. Based on QuickLogic's patented  $ViaLink^{\mathbb{R}}$  technology (see **Figure 2**), this fabric provides a highly compact, low-power resource that can implement virtually any logic function the development team requires. The fabric is non-volatile, so once programmed it does not need any external memory-based boot source nor does it suffer any start-up delay. Simply speaking, it functions just as hard logic would.

www.quicklogic.com © 2010 QuickLogic Corporation

4

Figure 2: Patented ViaLink technology provides the basis for programmable fabric that yields compact, non-volatile circuitry with low-power demands.

The programmable fabric gives the CSSP a degree of flexibility unmatched in ASSPs. QuickLogic supports the programmable fabric with an extensive library of functional building blocks, including processor interfaces, from which development teams can choose for implementing their unique design requirements. These tested and proven system blocks (PSBs) are optimized for the programmable fabric, providing high performance while requiring a minimum of resources. These library resources help ensure that custom designs can be implemented in a CSSP with a minimum amount of design time and effort.

The overall CSSP concept effectively acts as a companion solution to the Application or Baseband processor in a mobile system. QuickLogic takes full responsibility for the integration of the PSBs into our solution platforms to achieve the complete solution.

QuickLogic's CSSP solution platforms are market-specific design platforms, each targeting a specific mobile device market. The platforms implement, in hard logic blocks, the baseline features and standard variations the mobile device needs to offer. The programmable fabric provides additional resources for adding product differentiation features as well as implementing new standard features that the market comes to demand. As a result, a CSSP platform can serve as the hardware basis for a unique device design, regional variations on that design, and subsequent generations of the design that incorporate additional features.

The customer specific features and benefits include:

- Customized to meet all client specifications

- Fast time-to-market and low design risk

- Highly integrated and differentiated products

The application specific features and benefits include:

- Programmable platforms optimized for low power

- Flexible, customizable PSBs

- Low cost and small footprint

# **Designing with CSSPs**

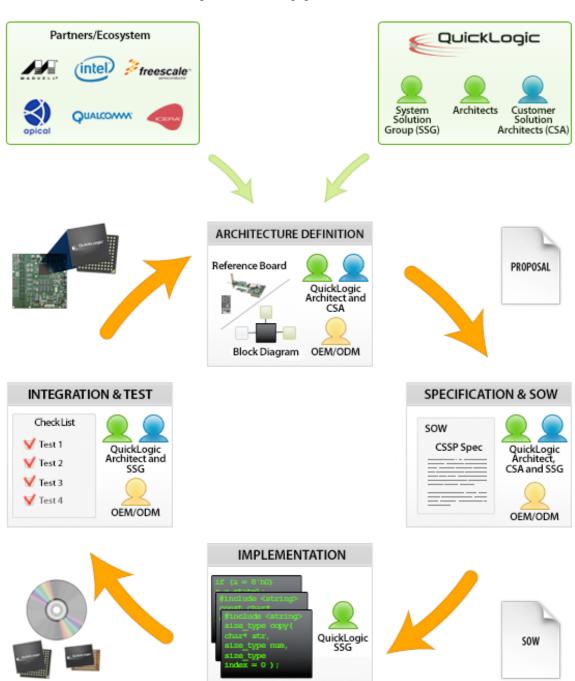

The design process for utilizing a CSSP speeds the mobile device's time-to-market and minimizes the customers' design effort and risk. QuickLogic CSSP architects work with the customer's development team to define the specifications for their unique CSSP device. Then, QuickLogic's internal System Solution Group (SSG) chooses one of the available CSSP solution platforms available as stock components in the PolarPro<sup>®</sup>, PolarPro II, or ArcticLink<sup>®</sup> II solution platform families and implements a design to meet the specifications. QuickLogic delivers packaged and tested CSSP components, fully programmed with the customer's custom design, in whatever volumes are required.

The CSSP approach offers significant advantages to the mobile device design team. The approach provides proven functionality, yet is highly customizable, to provide product differentiation and variation. The compact nature of ViaLink technology, along with the hard logic blocks, ensures that the final design occupies a minimal footprint, keeping both component and board costs low. ViaLink also ensures that the design has a low power demand, supporting long battery life, because ViaLink does not require the use of active circuits to maintain the logic implemented in the programmable fabric.

A CSSP-based design represents low risk to the development team. Design times are short and do not require the customer to have in-house expertise. QuickLogic's SSG handles the detailed design steps. Inventory risks are minimal because fabricating the customized CSSP requires only electrical programming of a stock wafer, final test, and packaging. This allows QuickLogic to support buffer stock and respond to demand by drawing from a die bank rather than starting the production of new wafers. Customers only order as many finished devices as they currently need yet are ensured that upside demands can be quickly met.

#### **CSSP Platform Families**

QuickLogic currently offers four CSSP solution platform families: the PolarPro, PolarPro II, and ArcticLink II families. All offer combinations of hard logic blocks and a programmable fabric designed for power-sensitive mobile devices.

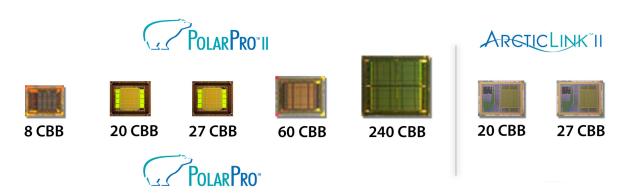

The PolarPro and PolarPro II families offer designers a wide range of size, performance, and cost options. The family's hard logic blocks include high speed, flexible dual-port RAM blocks and configurable synchronous/asynchronous FIFO controller blocks. These families also offer a processor interface that is optimized in the programmable fabric for performance, CPU utilization, and battery life. Family members provide a wide range of fabric capacities, from 8 to 240 Customizable Building Blocks (CBBs), and are available in small form-factor packaging or as known-good-die to address space-constrained applications (see Figure 3).

The ArcticLink II solution platform family integrates the second generation Visual Enhancement Engine (VEE) and Display Power Optimizer (DPO) technologies, along with optional MDDI Type 2 Client with PHY, MIPI DSI, CellularRAM Frame Buffer and Programmable Fabric. This highly integrated, yet flexible architecture makes it the ideal platform to implement Customer Specific Standard Product (CSSP) solutions in the display and connectivity subsystems of Smartphones, Smartbooks, Netbooks, Mobile Internet Devices (MIDs), and other portable devices. The MDDI client enables use with Qualcomm's latest Mobile Station Modem™ (MSM™) MSM7xxx-series and MSM8xxx-series mobile processors, including the Snapdragon family. The RGB and/or MIPI DSI interface allow for use with other mobile processor and display architectures.

www.quicklogic.com © 2010 QuickLogic Corporation

Figure 3: The QuickLogic PolarPro, PolarPro II, ArcticLink and ArcticLink II Solution Platforms offer a wide range of fabric capacities.

Along with allowing the incorporation of unique features into the CSSP, the programmable fabric blocks offer development teams an opportunity to extend the device's standard function offering where needed. To support the rapid and efficient implementation of standard functions into the fabric, QuickLogic offers a substantial library of PSBs. These blocks have been tested and are optimized for performance and efficient use of the programmable fabric resources.

# **Full System Design Support**

QuickLogic realizes that, in today's design environment, a component by itself does not fully meet a development team's needs. Hardware design support, software drivers, and packaging are also critical needs that vendors must address. QuickLogic provides a full range of services and libraries to address these needs as well.

On the hardware development front, QuickLogic supports customers in two ways. First, its Customer Solutions Architects (CSAs) help development teams determine the best way to utilize a CSSP platform in their design. Working closely with the development team's designers, the CSAs help create detailed specifications for the functionality and performance of a customized CSSP.

Once the specifications are complete, QuickLogic's SSG steps in to implement the design. The SSG handles the details of configuring the personality of hard logic blocks, implementing additional standard functions in the programmable fabric, and implementing the customer's unique functions in the fabric. Support from the SSG carries through the design phase into test and system integration. SSG members work along side customer development team members at the customer site to ensure that the customized CSSP functions as intended. The CSSP engagement model is shown in **Figure 4**.

Figure 4: CSSP Engagement Model

To aid a development team's software development effort, QuickLogic supports its CSSPs and PSBs with a full range of device drivers. Drawing on its experience with operating systems such as Windows Mobile<sup>®</sup>, Android, and Linux<sup>®</sup>, among others, QuickLogic has created drivers for each operating system for every block. The drivers are optimized for the CSSP implementation and are fully supported during the customer's hardware/software integration phase.

© 2010 QuickLogic Corporation

# **Packaging Requirements**

Hardware and software design command much of a development team's attention, but packaging is also a critical design aspect. The package that a CSSP component occupies can affect the final product's size, the amount of circuit board space used, and board costs. It can also impact decisions on what features to implement in the design when adding capability means using a larger die.

QuickLogic works with industry-leading package vendors to offer its CSSP platforms in state-of-the-art housings. This allows CSSPs to be available in bare die, Wafer Level Chip Scale packaging (WLCSP), or in a variety of packaging sizes, including sizes as small as  $3.25 \times 3.5$  mm,  $6 \times 6$  mm,  $8 \times 8$  mm, and  $12 \times 12$  mm surface mount styles (see **Figure 5**). Working closely with packaging vendors also allows QuickLogic to customize packaging for a customer's needs. A design implemented in one member of a CSSP solution platform family, for instance, can be ported to another member with more resources in order to add functionality, yet be packaged in the same housing as the original design. This option allows development teams to upgrade their design's functionality without impacting the board layout or size. If the design upgrades do not require additional I/O, the new CSSP can even have the same pin-out as the original.

Figure 5: Packaging options within the CSSP families ensure that development teams can meet their design space requirements and offer low-impact upgrade possibilities.

This level of packaging flexibility as well as the design flexibility of the CSSP is essential for today's mobile device designs. Development teams need solutions that offer high performance, complex functionality, and design flexibility all at low risk with quick results. Platform-based design provides such solutions, and QuickLogic's CSSP platforms address the full range of developer needs. Customers define the requirements that their customized CSSP component must meet, and QuickLogic provides the design along with software and integration support. Mobile device designers face considerable challenges, but with QuickLogic's CSSP approach, those challenges have been solved – Your idea, Our platform, Customized for you.

#### **Contact Information**

Phone: (408) 990-4000 (US)

(647) 367-1014 (Canada) +(44) 1932-21-3160 (Europe) +(886) 2-2345-5600 (Taiwan) +(86) 21-5116-0532 (China)

E-mail: info@quicklogic.com

Sales: America-sales@quicklogic.com

Europe-sales@quicklogic.com

Asia-sales@quicklogic.com

Japan-sales@quicklogic.com

Support: www.quicklogic.com/support

Internet: www.quicklogic.com

## **Revision History**

| Revision | Date           | Originator and Comments                                              |

|----------|----------------|----------------------------------------------------------------------|

| Α        | August 2007    | First release                                                        |

| В        | September 2007 | Judd Heape, Howard Li, and Kathleen Murchek                          |

| С        | January 2009   | Kathleen Murchek                                                     |

| D        | September 2009 | Brian Faith and Kathleen Murchek                                     |

| E        | August 2010    | Paul Karazuba and Kathleen Bylsma                                    |

| F        | September 2010 | Brian Faith and Kathleen Bylsma Update PSBs in Intelligence section. |

#### **Notice of Disclaimer**

QuickLogic is providing this design, product or intellectual property "as is." By providing the design, product or intellectual property as one possible implementation of your desired system-level feature, application, or standard, QuickLogic makes no representation that this implementation is free from any claims of infringement and any implied warranties of merchantability or fitness for a particular purpose. You are responsible for obtaining any rights you may require for your system implementation. QuickLogic shall not be liable for any damages arising out of or in connection with the use of the design, product or intellectual property including liability for lost profit, business interruption, or any other damages whatsoever. QuickLogic products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use QuickLogic products in these types of equipment or applications.

QuickLogic does not assume any liability for errors which may appear in this document. However, QuickLogic attempts to notify customers of such errors. QuickLogic retains the right to make changes to either the documentation, specification, or product without notice. Verify with QuickLogic that you have the latest specifications before finalizing a product design.

© 2010 QuickLogic Corporation

# **Copyright and Trademark Information**

Copyright © 2010 QuickLogic Corporation. All Rights Reserved.

The information contained in this document is protected by copyright. All rights are reserved by QuickLogic Corporation. QuickLogic Corporation reserves the right to modify this document without any obligation to notify any person or entity of such revision. Copying, duplicating, selling, or otherwise distributing any part of this product without the prior written consent of an authorized representative of QuickLogic is prohibited.

QuickLogic, ArcticLink, PolarPro, the PolarPro design, and ViaLink are registered trademarks, the QuickLogic logo is a trademark of QuickLogic. Other trademarks are the property of their respective companies.