QuickLogic has been supplying FPGA-based products for consumer, industrial and mission-critical applications for nearly three decades. The company’s embedded FPGA (eFPGA) initiative offers SoC designers the flexibility to easily implement post-production changes, thus providing the benefit of hardware programmability to their end customers. Multiple chip variants can be created from a single mask set, enabling customization to address fragmented and/or rapidly evolving standards.

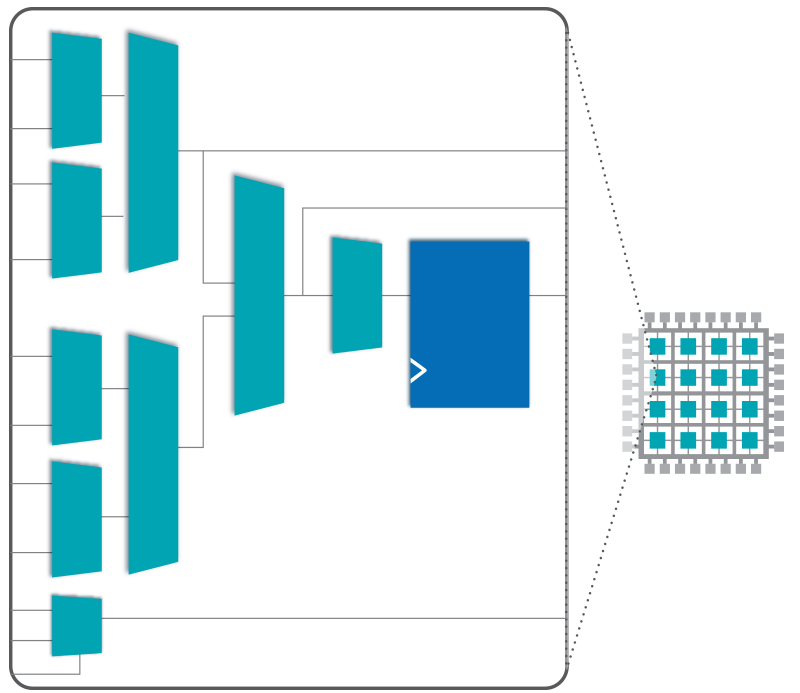

A collection of basic cells, namely a logic cell, or in some architectures a look up table (LUT)

An efficient routing network for regular signals as well as high fanout signals such as clocks and reset signals

Test circuitry to ensure that the programmable elements are fully operational

Programming circuitry

The hardware technology alone is not very useful without the EDA software, which efficiently targets the hardware to extract the maximum performance and utilization of the FPGA.

The FPGA software technology requires the following:

QuickLogic has been working with FPGA technology for the last 30 years, and has invested heavily in FPGA architecture research and development, and most importantly, building the software tools to efficiently map HDL designs into the FPGA.

Our approach to our architecture has been an evolutionary process, as we have shipped millions of units to customers. Each iteration of our software includes improvements in order to achieve the optimal efficiency that FPGA users expect.

In addition to building the FPGA block, we have been creating SoC solutions that are comprised of eFPGAs + CPUs + ASIC content since 1999. Our devices have been increasingly sophisticated, incorporating the latest technology across multiple nodes.

Available Technologies: |

||

|---|---|---|

| Architecture | Benefit | Available Process |

|

ArcticPro |

Lowest power consumption eFPGA in the market, suitable for SoCs targeted at battery-operated systems | GlobalFoundries 65nm, 40nm,SMIC 40nm, TSMC 40nm |

|

ArcticPro 2 |

General-purpose eFPGA, mid-range density, suitable for ML and IoT applications at the edge | GlobalFoundries 22FDX, TMSC 28nm |