Aurora Software Tool Suite for eFPGA Design

Comprehensive Tool Suite with Complete Support for eFPGA Design

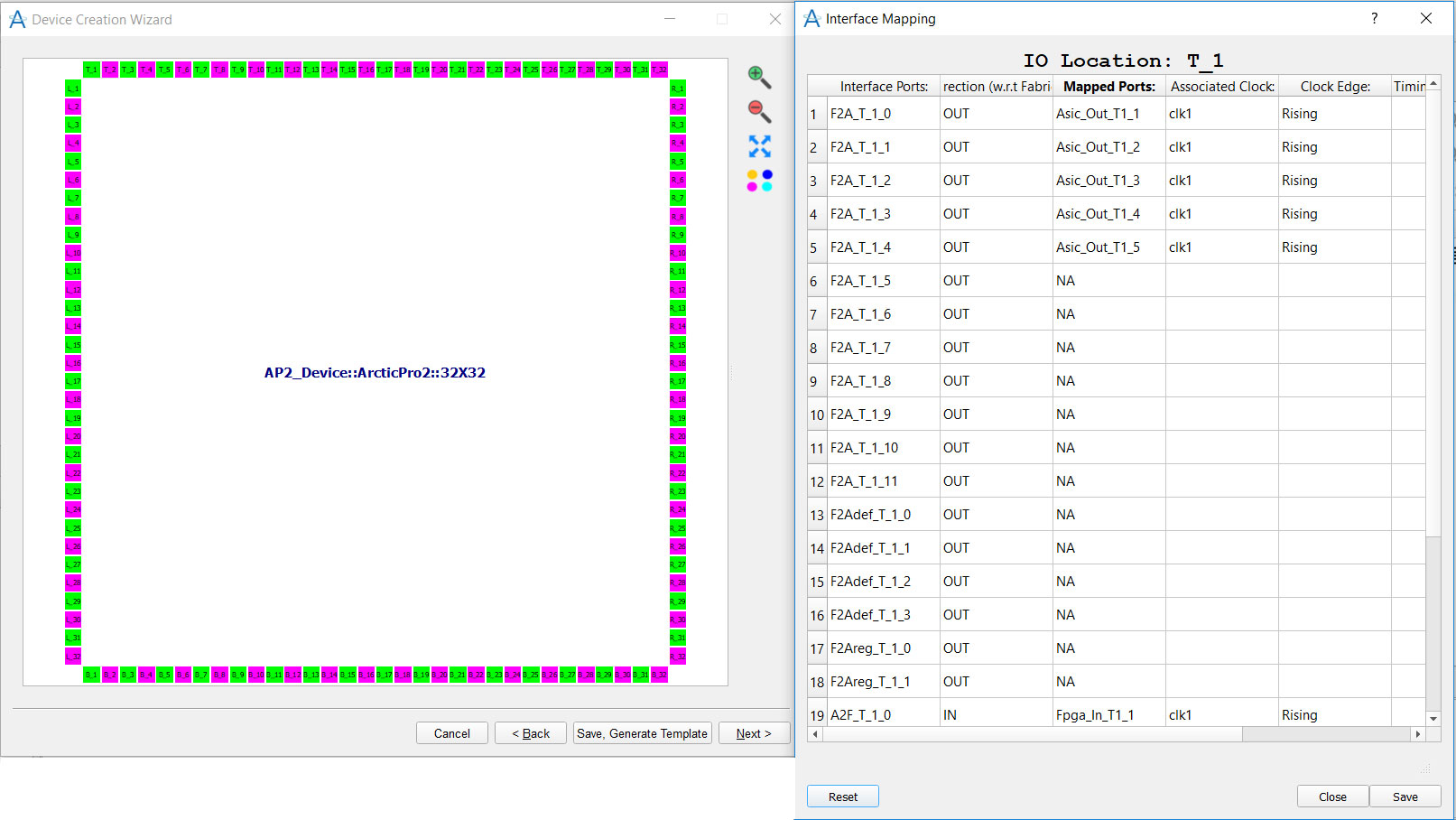

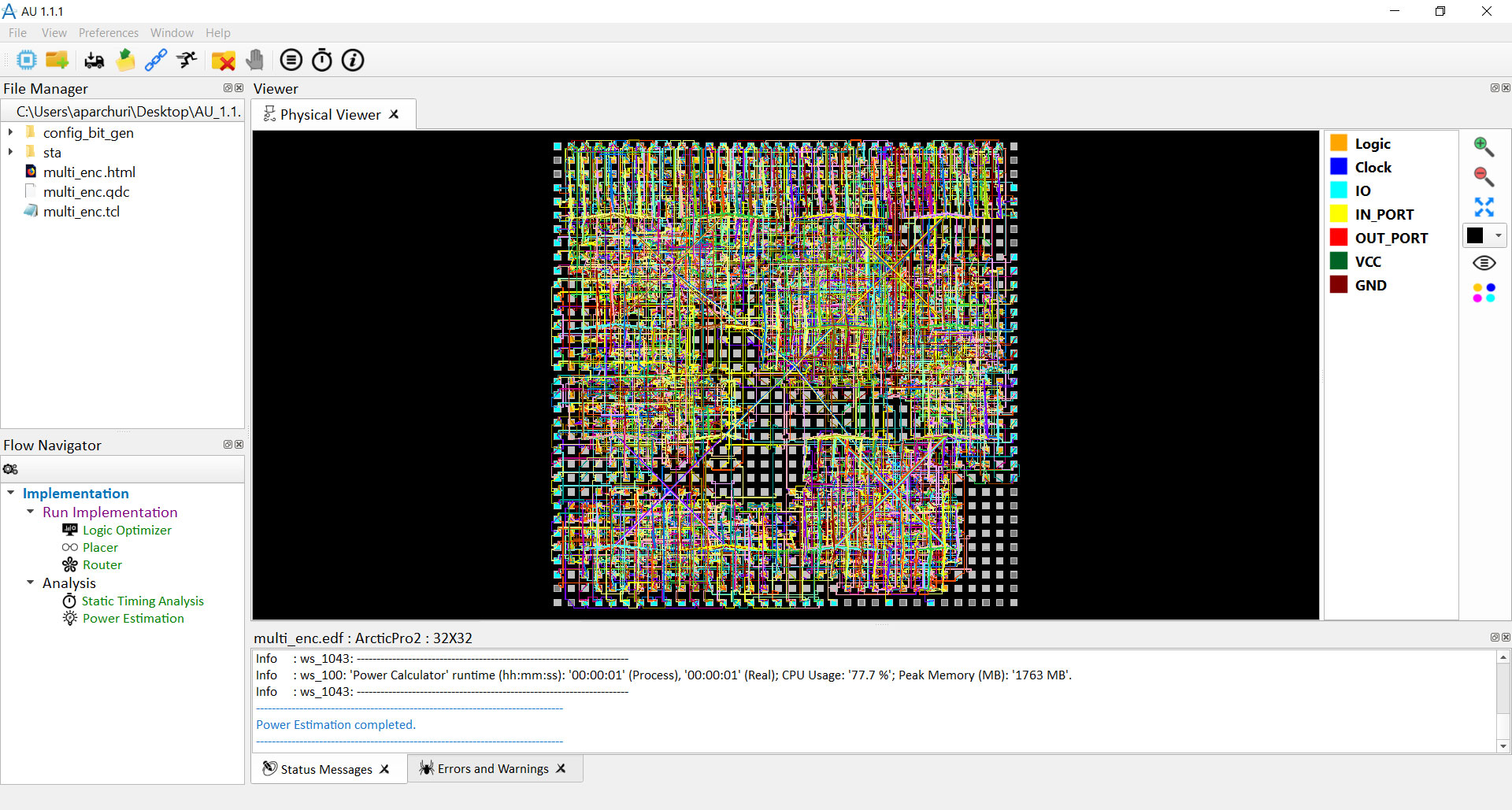

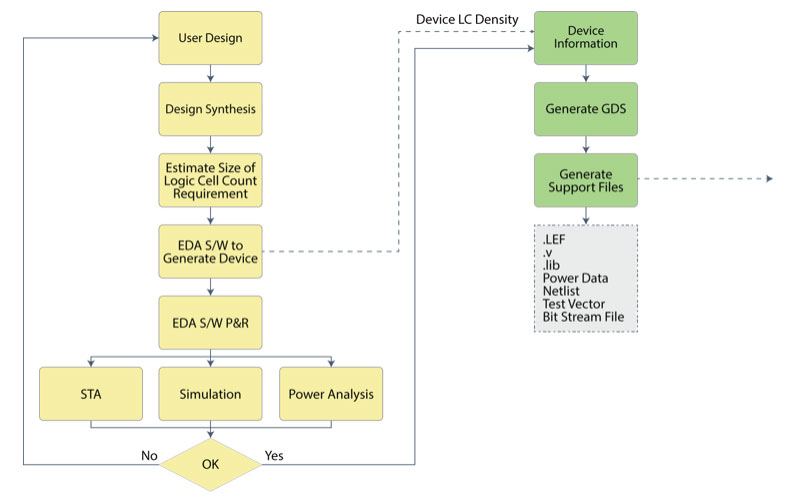

The Aurora Software Tool Suite is a comprehensive software tool suite designed for eFPGA design. With its device creation flow and proven Place & Route implementation flow, designers can create their own eFPGA device, and complete their designs through the implementation flow in the eFPGA. Aurora supports the ArcticPro and ArcticPro 2 architectures and with seamless integration with Mentor Graphics Precision, guarantees the designer optimal netlist and P&R results.